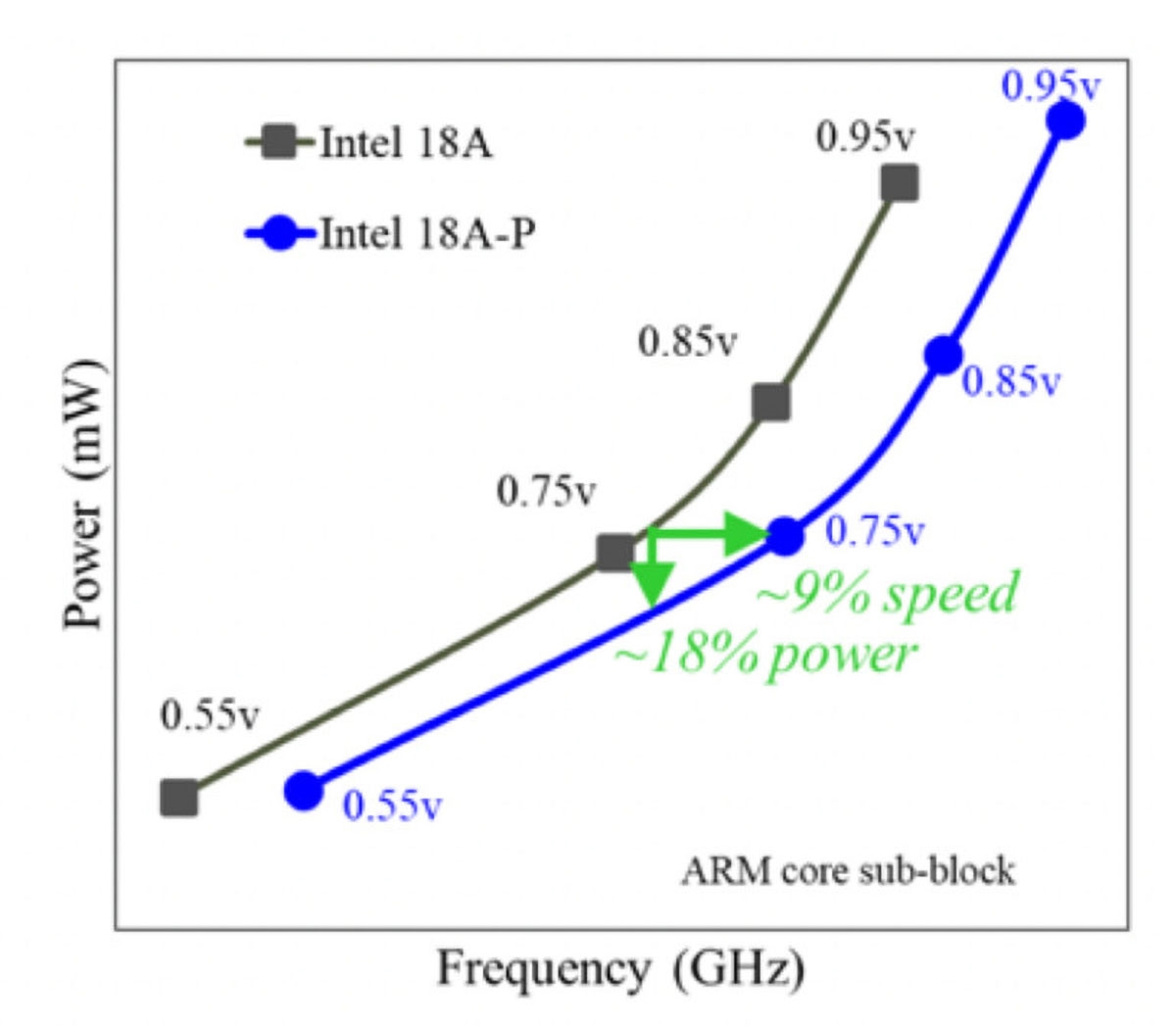

Intel официально объявила ключевые технические данные технологического узла Intel 18A-P в документе T1.2 на семинаре VLSI 2026, проходившем в Гонолулу, Гавайи. По сравнению со стандартным узлом Intel 18A, 18A-P обеспечивает прирост производительности более чем на 9 % при том же энергопотреблении и снижает энергопотребление более чем на 18 % при той же производительности.

Таких улучшений производительности и мощности, которые обычно наблюдаются только при переходе узлов между поколениями, теперь можно достичь с помощью 18A-P той же плотности.

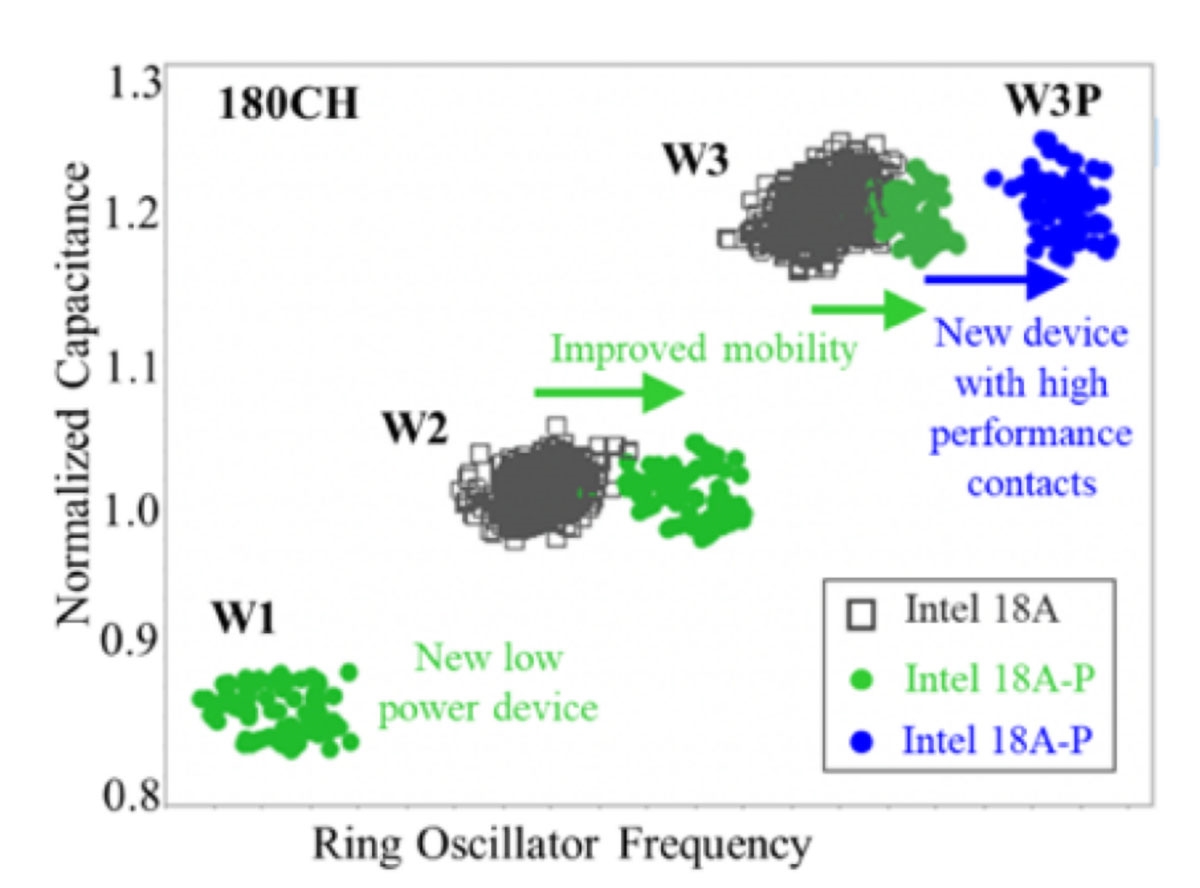

В исходном документе Intel перечислены четыре конкретных улучшения: дополнительные логические пары ТН, более жесткий контроль угла смещения тактовой частоты, новые устройства с низким энергопотреблением в библиотеках высокой плотности (HD) и высокой производительности (HP), а также версии устройств HP с повышенной производительностью в обеих библиотеках.

Intel сузила углы перекоса 18A-P примерно на 30% по сравнению со стандартным 18A. Разница в производительности между транзисторами на одной пластине значительно снижается, энергопотребление и рабочие характеристики становятся более предсказуемыми, одновременно улучшаются выход параметров и согласованность чипа.

Что касается рассеивания тепла, термическое сопротивление 18A-P примерно на 50% ниже, чем у 18A, а эффективность теплопроводности значительно улучшена. Это особенно важно для устойчивой высокочастотной работы в сценариях высокопроизводительных вычислений, а также напрямую реагирует на проблемы рассеивания тепла, возникающие из-за технологии заднего источника питания (PowerVia).

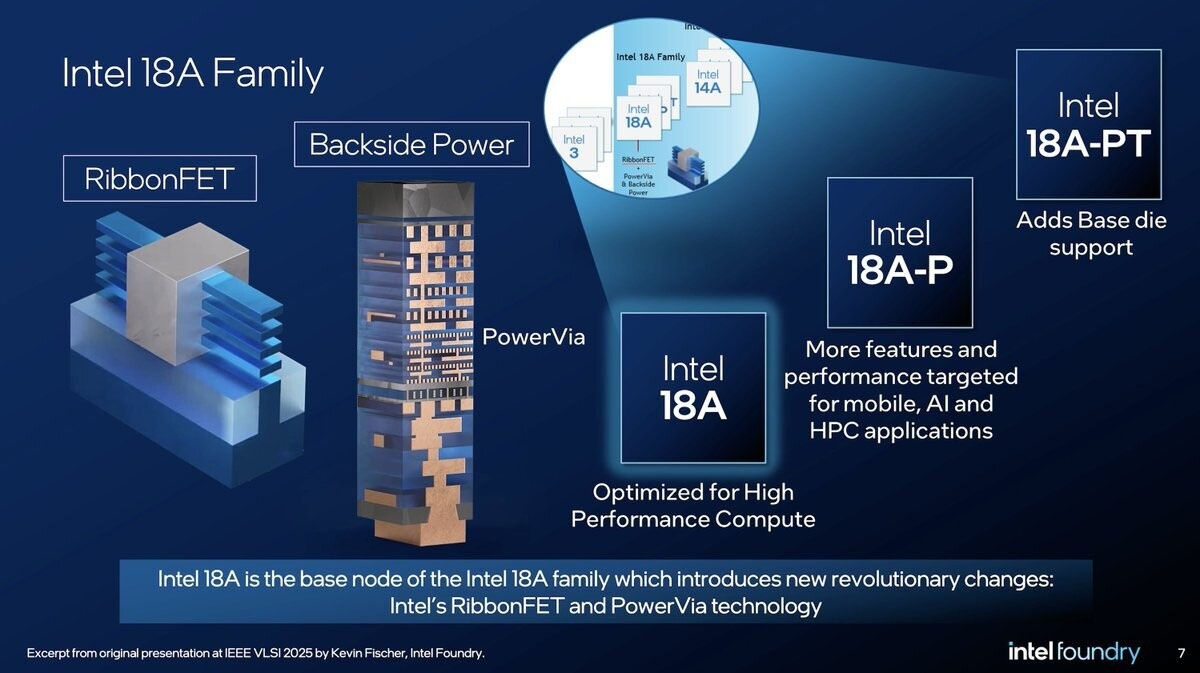

Intel отправила потенциальным клиентам версию 1.0 своего комплекта проектирования процессов PDK для 18A-P, чтобы они могли начать тестирование проверки микросхем. Этот процесс по-прежнему основан на универсальной архитектуре затворных транзисторов RibbonFET и технологии обратного питания PowerVia и представляет собой версию платформы 18A с улучшенными характеристиками.

По данным TrendForce, Apple рассматривает возможность использования процесса 18A-P для производства чипов серии M, а Google рассматривает возможность использования передовой технологии упаковки Intel EMIB для продвижения проекта TPU v8e. Сопутствующие продукты могут быть запущены уже в 2027 году.